- Obecnie brak na stanie

Arria V GX FPGA Video Development System

darmowa wysyłka na terenie Polski dla wszystkich zamówień powyżej 500 PLN

Jeśli Twoja wpłata zostanie zaksięgowana na naszym koncie do godz. 11:00

Każdy konsument może zwrócić zakupiony towar w ciągu 14 dni bez zbędnych pytań

Overview

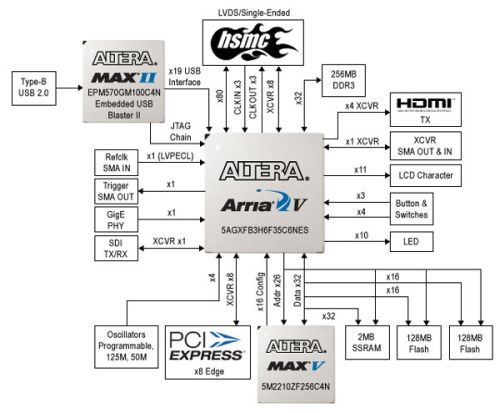

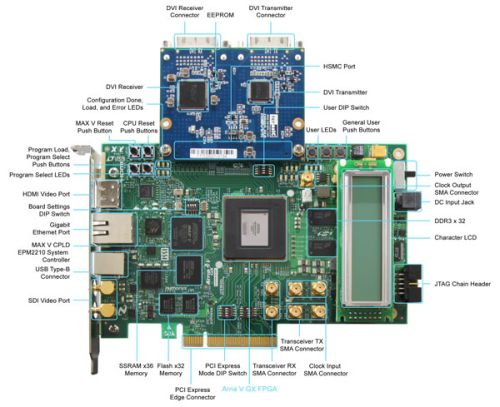

The Arria V GX FPGA Video Development System is an ideal video processing platform for high-performance, cost-effective video applications. The Arria II development kit features 256MB of SDRAM memory, HDMI, and SDI connections to form a perfect solution for imaging applications.

The DVI-HSMC daughter card part of the bundled package will allow developers to access high quality and high resolution video signals that can support resolution up to 1600x1200. A complete DVI video controller design with source code is provided.

Terasic recognized for its strong design expertise in high-end video, imaging and multimedia products have made available a video development package that targets video processing development. The platform can also allow users to experience advanced image processing designs incorporating VIP (Altera’s Video and Image Processing Suite MegaCore Functions).

Specification

Altera Arria V GX Video Development System

Terasic DVI-HSMC Card

Layout

Resources

Demo

DVI Video Development System Bundle

The Terasic DVI Development System bundles together the DVI daughter card and Altera development kit for cost-effective video development. All source code shown is included.

Code: K0111

NanoPi Duo2 to niewielka płytka wyposażona w układ SoC Allwinner H3, pamięć RAM o pojemności 256MB oraz wbudowany moduł WiFi/Bluetooth. Na port GPIO wyprowadzono m.in. interfejs Ethernet, USB, SPI, UART, I2C. FriendlyELEC NanoPi Duo2

Brak towaru

Brak towaru

Brak towaru

Zmontowany nieskomplikowany termometr - rejestrator. AVT5573 C

Brak towaru

Dual High-Speed Low-Noise Operational Amplifier, SOIC8, Texas Instruments, RoHS

Brak towaru

Brak towaru

Shield dla STM32 Nucleo z modułem WiFi b/g/n SPWF01SA. Firmware modułu pozwala na pracę jako klient oraz serwer UDP/TCP, serwer WWW, obsługuje protokoły TCP/IP, TLS/SSL. Dostępnych jest 16 linii GPIO

Brak towaru

Niewielkich rozmiarów silnik firmy Pololu z enkoderem 48 CPR, kompatybilny z przekładniami 25D mm, standardowym napięciem pracy 12 V i prędkością 5600 rpm. Pololu 3260

Brak towaru

Moduł audio ze wzmacniaczem stereo dużej mocy wyposażony w Bluetooth 5.0, który umożliwia bezprzewodowe odtwarzanie muzyki. Może obsługiwać głośniki o mocy od 50 W do 300 W i impedancji od 4 Ω do 8 Ω. DFRobot DFR0777

Brak towaru

Zestaw dystansów i złączy do rozbudowy robota Pololu 3pi. Nie zawiera płytki PCB. Pololu 1039

Brak towaru

Brak towaru

Brak towaru

Płytka PCB i zaprogramowany układ do prostego sterownika unipolarnego silnika krokowego. AVT1814 A

Brak towaru

Brak towaru

Brak towaru

Brak towaru

Arria V GX FPGA Video Development System