698,63 zł Netto

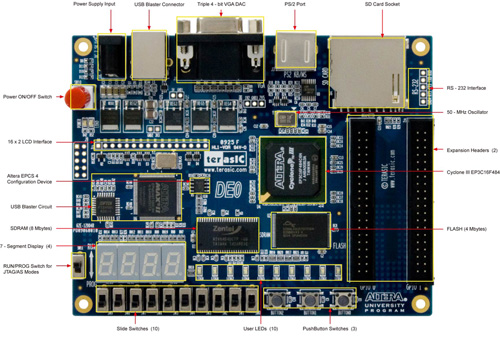

[CENA EDUKACYJNA] Zestaw ewaluacyjny Terasic DE0 Board dla układów FPGA Cyclone III firmy Altera. Wyposażono go we wszystkie podstawowe peryferia umożliwiające prowadzenie prac badawczych i ewaluacyjnych z układami FPGA, w tym programator-konfigurator JTAG. Obniżona cena (w stosunku do klasycznej wersji Terasic DE0) dotyczy wyłącznie szkół, uczelni, wykładowców, uczniów i studentów.

darmowa wysyłka na terenie Polski dla wszystkich zamówień powyżej 500 PLN

Jeśli Twoja wpłata zostanie zaksięgowana na naszym koncie do godz. 11:00

Każdy konsument może zwrócić zakupiony towar w ciągu 14 dni bez zbędnych pytań

Oferta przeznaczona wyłącznie dla odbiorców akademickich (studentów i wykładowców wyższych uczelni)!

Składając zamówienie należy podać:

- imię i nazwisko użytkownika

- stanowisko

- adres e-mail użytkownika (adres e-mail musi być z domeny uczelni)

- pełną nazwę uczelni

- nazwę wydziału/instytutu/zakładu dydaktycznego

- adres uczelni

- stronę internetową uczelni

- telefon

- zastosowanie produktu

W uzasadnionych przypadkach zastrzegamy sobie prawo do odmowy zrealizowania zamówienia z oferty akademickiej.

Wszelkie zapytania można kierować na adres: sprzedaz@kamami.pl.

The DE0 Development and Education board is designed in a compact size with all the essential tools for novice users to gain knowledge in areas of digital logic, computer organization and FPGAs. It is equipped with Altera Cyclone III 3C16 FPGA device, which offers 15,408 LEs. The board provides 346 user I/O pins, and is loaded with a rich set of features that makes it suitable to be used for advanced university and college courses, as well as the development of sophisticated digital systems. The DE0 combines the Altera low-power, low-cost, and high performance Cyclone III FPGA to control the various features of the DE0 Board. The DE0 Development Board includes software, reference designs, and accessories required to ensure the user simple access in evaluating their DE0 Board.

Resources

|

DE0 Debounce Project contains a new DE0 top Quartus project with debounce IP, as well as a DE0 debounce |

Kit Contents

The DE0 package includes:

Code: P0037

Wyświetlacz LCD alfanumeryczny 2x16 bez podświetlenia przeznaczony do zestawów firmy TerasIC (DE0, DE1, DE2 , DE2 -115). P0075

TerasIC LT24 to moduł z wyświetlaczem LCD 2,4-calowym o rozdzielczości 320 x 240 pikseli. Wyświetlacz wyposażony jest w panel dotykowy rezystancyjny. Wyświetlacz przeznaczony jest do użycia z zestawami uruchomieniowymi TerasIC ze złączem GPIO 2x20. P0185

Płytka deweloperska z układem FPGA ALTERA Cyclone IV EP4CE6E22C8N. Waveshare CoreEP4CE6

Brak towaru

Zestaw z płytką FPGA Terasic DE10-Nano oraz modułem WiFi. Przeznaczony do projektów wykorzystujących FPGA do pracy w chmurze. TerasIC P0700

Brak towaru

Zestaw rozwojowy z układem FPGA Altera MAX10 (10M50DA) z wbudowaną pamięcią Flash i złączami rozszerzeń interfejsu IO. Numato Lab NLFA1002B

Brak towaru

Brak towaru

Płytka rozwojowa FPGA Altera Cyclone IV EP4CE6E22C8N w zestawie z płytką bazową. Waveshare OpenEP4CE6-C Standard

Brak towaru

Płytka rozwojowa FPGA Altera Cyclone IV EP4CE6E22C8N w zestawie z płytką bazową i modułami rozszerzeń. Waveshare OpenEP4CE6-C Package A

Brak towaru

Kompaktowy zestaw FPGA z układem Intel Arria 10 GX wyposażony w 8 GB pamięci DDR4-2133 oraz złącze komunikacyjne Thunderbolt 3. Może być zastosowany bezpośrednio na laptopach lub innych urządzeniach przenośnych. Terasic FLIK P0642

Brak towaru

Brak towaru

Altera DE2-115 Development and Education Board Academic

Zestaw startowy DE10-Nano Kit z układem System-on-Chip z rodziny Cyclone V SoC, w którym zintegrowano m.in. dwurdzeniowy procesor ARM Cortex-A9 oraz dużą matrycę FPGA. Zestaw wyposażono w programator-konfigurator-debugger JTAG. Terasic P0496

Brak towaru

Zestaw rozwojowy z układem FPGA Altera MAX10 (10M16DA) z wbudowaną pamięcią Flash i złączami rozszerzeń interfejsu IO. Numato Lab NLFA1001A

Brak towaru

Zestaw startowy DE10-Standard z układem System-on-Chip z rodziny Cyclone V SoC, w którym zintegrowano m.in. dwurdzeniowy procesor ARM Cortex-A9 oraz dużą matrycę FPGA. Zestaw wyposażono w programator-konfigurator-debugger JTAG. P0493

Moduł ewaluacyjny z procesorem Intel Stratix 10 SoC z elementami logicznymi 2800K. Moduł posiada pamięć DDR4 SDRAM (do 64 GB), wbudowany USB-Blaster II, Ethernet, microSD, miniUSB oraz złącza FMC/FMC+ do rozbudowy. TerasIC Apollo S10 SoM Board (P0630)

Brak towaru

Płytka rozwojowa FPGA Altera Cyclone IV EP4CE6E22C8N w zestawie z płytką bazową i modułami rozszerzeń. Waveshare OpenEP4CE6-C Package B

Brak towaru

Moduł SoM z układem SoC łączącym FPGA z rdzeniem ARM Cortex-A9. Płytka wyposażona jest w złacze DDR4 Eadge (z zasialniem 3,3 V). Terasic P0553

Brak towaru

[CENA EDUKACYJNA] Zestaw startowy FPGA wyposażony w Cyclone V GT z 301K LE i obsługuje PCIe Gen 2x4. Płytka posiada 1 GB pamięci DDR3, 64 MB pamięci SDRAM, interfejs UART-USB oraz rozszerzenia, takie jak GPIO i Arduino. Terasic P0559

Brak towaru

[CENA EDUKACYJNA] Zestaw ewaluacyjny Terasic DE0 Board dla układów FPGA Cyclone III firmy Altera. Wyposażono go we wszystkie podstawowe peryferia umożliwiające prowadzenie prac badawczych i ewaluacyjnych z układami FPGA, w tym programator-konfigurator JTAG. Obniżona cena (w stosunku do klasycznej wersji Terasic DE0) dotyczy wyłącznie szkół, uczelni, wykładowców, uczniów i studentów.